## Notice

Copyright of Thomas L. Floyd. Use in class only. Do not distribute unless permission is obtained from the original author.

- 2. 1 byte = 8 bits; 2 bytes = 16 bits

- Initially: 0000 1<sup>st</sup> CLK: 1000 2<sup>nd</sup> CLK: 1100 3<sup>rd</sup> CLK: 0110

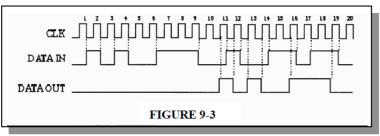

- 8. See Figure 9-3.

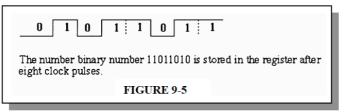

10. See Figure 9-5.

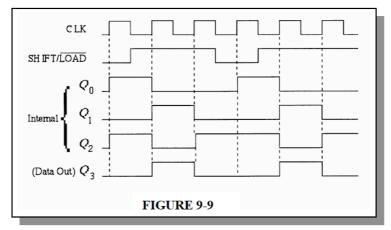

14. See Figure 9-9.

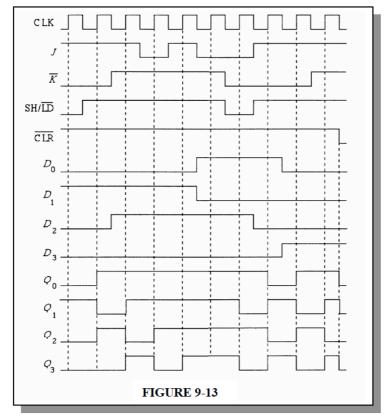

**18.** See Figure 9-13.

22.

| Initially (76) | 01001100 |             |

|----------------|----------|-------------|

| CLK 1          | 00100110 | Shift right |

| CLK 2          | 00010011 | Shift right |

| CLK 3          | 00001001 | Shift right |

| CLK 4          | 00010010 | Shift left  |

| CLK 5          | 00100100 | Shift left  |

| CLK 6          | 01001000 | Shift left  |

| CLK 7          | 00100100 | Shift right |

| CLK 8          | 01001000 | Shift left  |

| CLK 9          | 10010000 | Shift left  |

| CLK 10         | 00100000 | Shift left  |

| CLK 11         | 00010000 | Shift right |

| CLK 12         | 00001000 | Shift right |

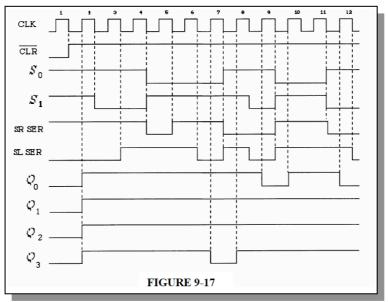

**24.** See Figure 9-17.

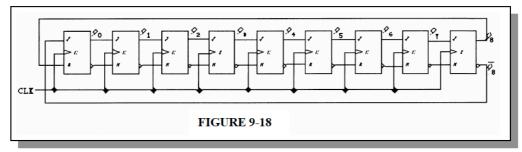

**26.** 2*n* = 18; *n* = **9** flip-flops

| $Q_0$ | $Q_1$ | $Q_2$ | $Q_3$ | $Q_4$ | $Q_5$ | $Q_6$ | $Q_7$ | $Q_8$ |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0     |

| 1     | 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 0     |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| 0     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| 0     | 0     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| 0     | 0     | 0     | 1     | 1     | 1     | 1     | 1     | 1     |

| 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 1     |

| 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

See Figure 9-18.

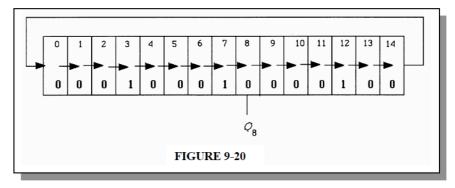

**28.** A 15-bit ring counter with stages **3**, **7**, and **12** SET and the remaining stages RESET. See Figure 9-20.